In weniger als einer Stunde entstanden:

Ein kompakter Skidbuffer, der nur das ready-Signal entkoppelt – ohne zusätzliche Latenz.

Hintergrund ist hier die Verwendung von AXI-like Handshaking und die Notwendigkeit, das ready-Signal zu entkoppeln, um die Datenverarbeitung zu optimieren. In den von mir genutzten Desisngs ist das ready-Signal oft der Flaschenhals, da es in der Regel durch mehrere Pipelines hindurch propagiert werden muss. Ein Skidbuffer kann hier helfen, die Latenz zu reduzieren und die Datenverarbeitung zu optimieren. Dagegen wird das valid-Signal nicht entkoppelt, da es durch jede Pipeline selbst entkoppelt wird.

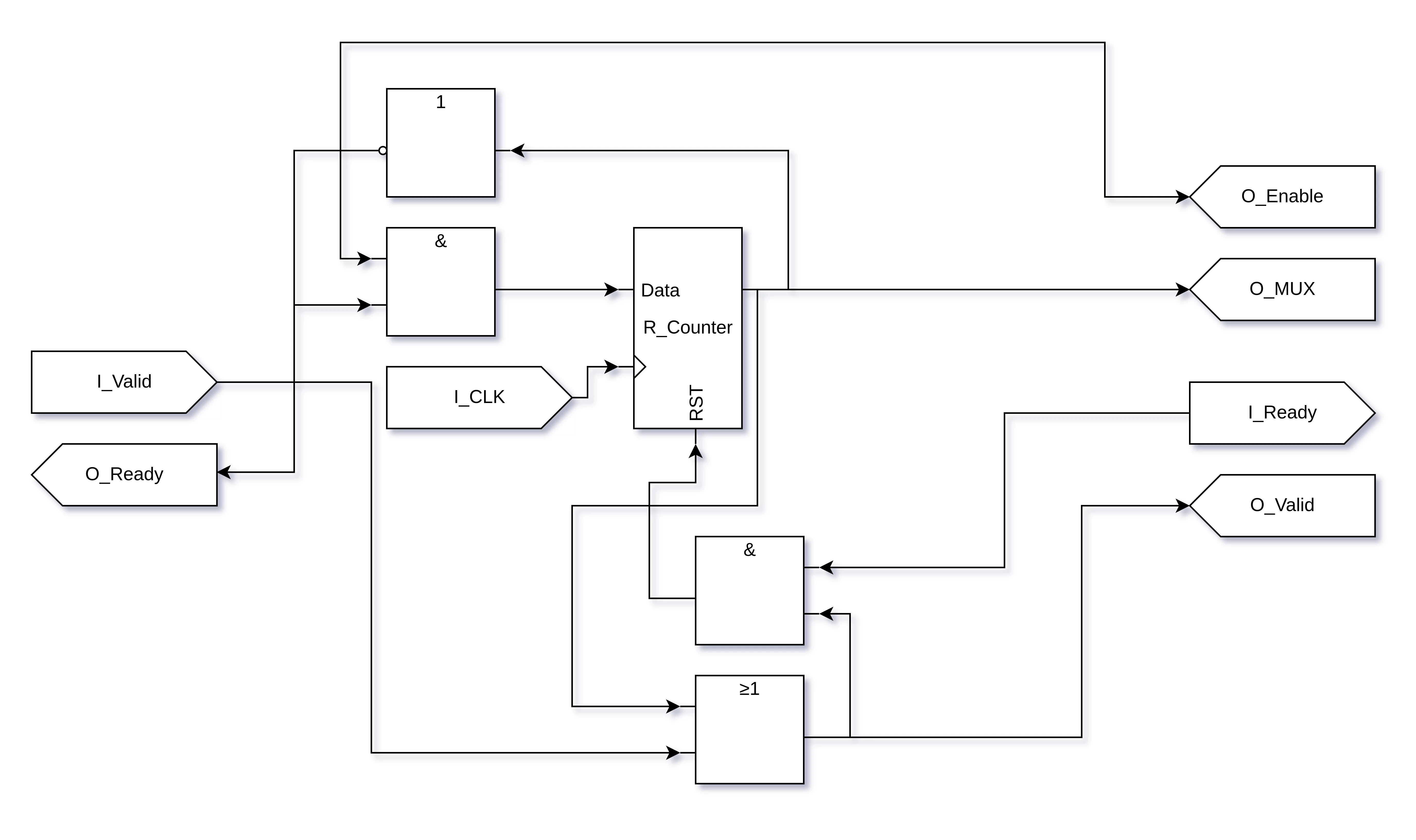

Das Design nutzt ein einfaches Prinzip:

- Wenn

ready = '1', wird direkt durchgeschaltet (MUX = 0) - Wenn

ready = '0', wird ein Zwischenspeicher aktiviert (MUX = 1) validbleibt entweder durchgeschliffen oder stammt aus dem Puffer

Das System erfüllt vollständiges AXI-like Handshaking

und wurde bei zufällig verzögertem Up- und Downstream erfolgreich getestet.

Ressourcenbedarf (nach Synthese, Xilinx Spartan-3):

- 1 Flipflop

- 4 LUTs

- 0 zusätzliche Latenz

| |

Die Architektur eignet sich besonders für tiefe Pipeline-Systeme mit Timing-Engpässen auf ready.

Kein Overhead – nur Datenfluss.