Created in less than an hour:

A compact skidbuffer that only decouples the ready signal – with zero added latency.

The background here is the use of AXI-like handshaking and the need to decouple the ready signal in order to optimize data processing. In the desisngs I use, the ready signal is often the bottleneck, as it usually has to be propagated through several pipelines. A skid buffer can help here to reduce latency and optimize data processing. In contrast, the ‘valid’ signal is not decoupled as it is decoupled by each pipeline itself.

Translated with DeepL.com (free version)

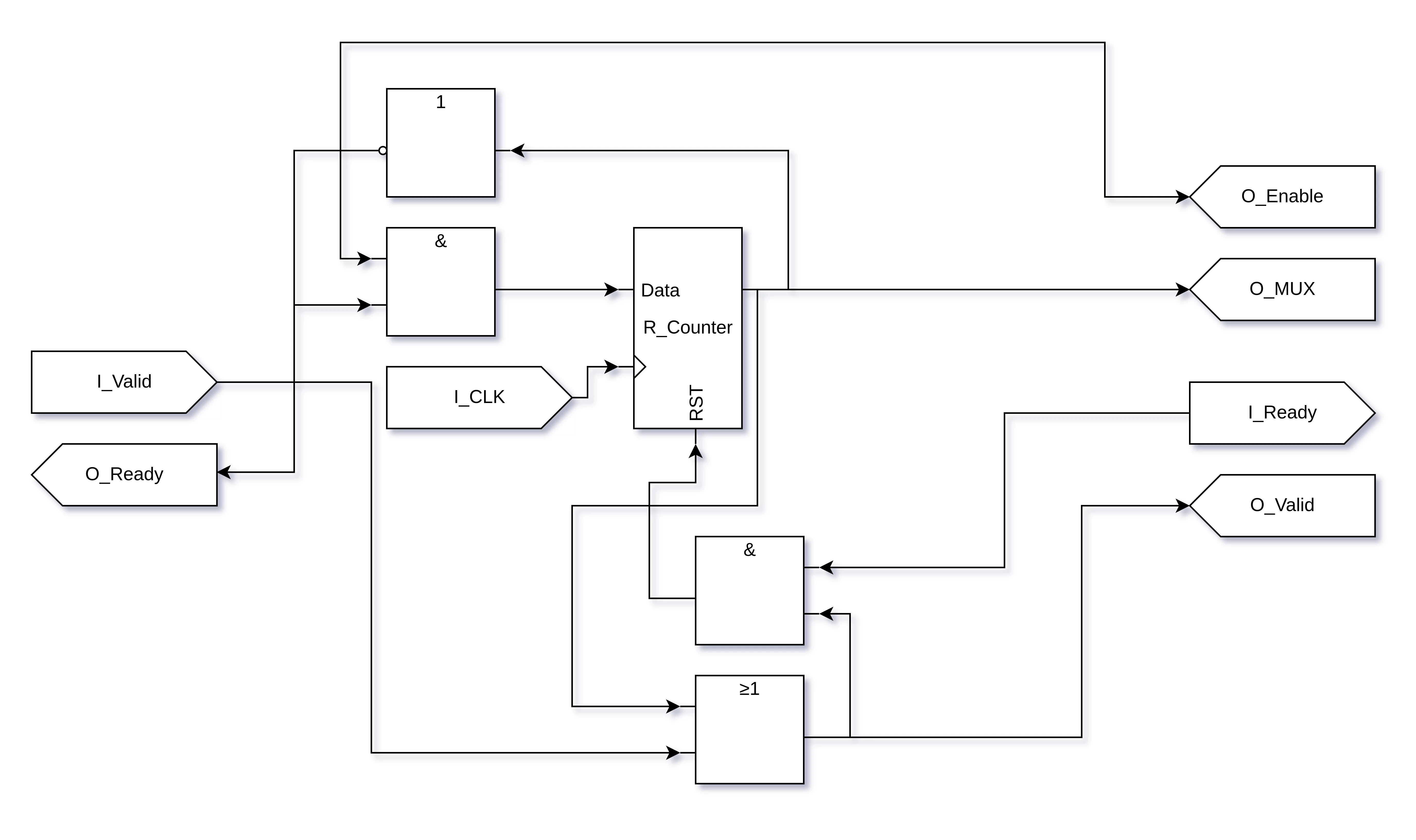

The design follows a simple principle:

- If

ready = '1', the signal is passed through directly (MUX = 0) - If

ready = '0', a buffer is activated (MUX = 1) validis either forwarded directly or taken from the buffer

The system implements complete AXI-like handshaking

and was successfully tested with randomly delayed upstream and downstream.

Resource usage (after synthesis, Xilinx Spartan-3):

- 1 flip-flop

- 4 LUTs

- 0 added latency

| |

This architecture is especially suited for deep pipeline systems with timing bottlenecks on ready.

No overhead – just data flow.